| Bus Basics |

| Written by Harry Fairhead |

| Sunday, 18 September 2022 |

|

Buses are everywhere and yes when you are looking for one they tend to come in threes! With that joke out of the way, let’s take a look at what a bus is in general and in particular. The Bus WordThe first question to answer is how did we get landed with the stupid sounding name “bus” for something so technically glamorous? The answer is that when they invented a vehicle which was supposed to be able to carry everyone from one place to another they called it an “Omnibus” which in Latin means “for all”. The “bus” part at the end of the word is one of the standard endings used in Latin but it grew beyond its importance in this case and the vehicle was eventually called a “bus”. This in turn became a word which was used to mean to transport something from place to place. Later the term “bus bar” was used by electricians to mean a bar of metal that transported electricity from one location to another. From here it was a small step to the modern use of “bus” to mean a set of connections that transports signals, or more abstractly data, from one place to another. Putting it as simply as possible, a bus is a set of wires that allows data to be transferred from one place to another. Sounds easy, what could possibly be difficult about a bus? The answer is quite a lot if you are trying to design one! A bus connects a device that is sending data and a device, or devices, which are receiving the data. Notice that a bus can have more than one receiving device but in general only one transmitting device is possible at any given moment. For the moment it is simpler if we concentrate on the situation where there is only one device in charge of the bus. The electronics of connecting to a bus is fairly straightforward and is accomplished by using buffer chips. Usually a bus will have an upper limit on the number of devices that can be connected to it and this is just a function of how much power the buffer chips can put into driving the bus. In addition there is almost certain to be a length restriction. The reason for this is to do with the way high-speed signals deteriorate as they travel down wires. The faster the data needs to move the more this effect becomes important and it explains why a bus cannot work at an arbitrarily high speed.

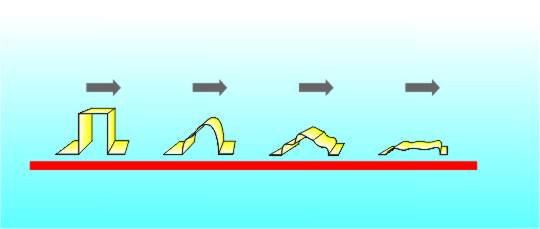

As a pulse travels down a wire it slowly degenerates until it is lost in the electrical noise

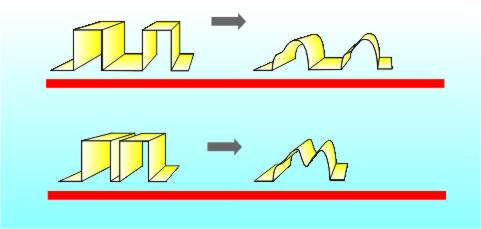

If two pulses are too close together then after travelling a short way you can’t tell that they are two pulses

The Big BusThere are many things that are important about a bus but the one that most users would list high is the capacity of the bus. Any given data connection has a limit in terms of the amount of data it can transfer in a given time. Typical units of bus capacity are Kbytes/s and Mbytes/s but you will also find, confusingly, Kbits/s and Mbits/s. The problem is when you see Kb/s does it mean thousands of bytes or bits per second? In general a lower case “b” means bits and an upper case “B” means bytes but you should always check if it isn’t obvious from the context. What matters in determining the data capacity of a bus is how many wires it has – its width – and how long it takes to transmit a single bit of data down one of the wires. As already discussed, this is limited by the physical design of the bus – there is a highest frequency pulse that will make it from one end of the bus to the other. In addition to this physical limitation there is also the problem of co-ordinating the data transfer. Generally there are additional lines in the bus that control the flow of data. There is often a read/write line that indicates the direction of data flow, a data valid signal and sometimes a data accepted signal.

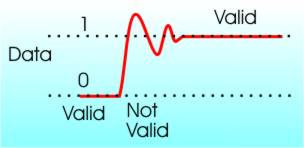

The signal on a bus cannot change instantaneously; it needs time to settle The usual sequence of events is that the device driving the bus puts data onto it by driving the bus lines high or low. It then waits for a fixed time for the bus to become stable and sets a “data valid” line high. At this point any device that is reading data from the bus can assume that it is ok to start reading it. As soon as the device is finished it sets a data accepted line which lets the driving device know that it can move on to the next data item. Notice that this description is very general and not of any particular bus. In practice they all do things slightly differently from one another in an effort to improve efficiency of data transfer or to provide additional sophistication. For example, if more than one device can drive the bus – become a “bus master” in the jargon – then you need extra signals to negotiate and determine who is the bus master at any moment. As soon as you start adding the needs of the real world a bus can begin to seem very complex but if you concentrate on what each part is doing in turn it never turns out to be that difficult. For example, the processor bus connects the memory to the processor but the control lines which select which memory location will be used are usually separated out in to a bus of their own – the address bus. In general the need to select which devices are active on the bus is the one that succeeds in complicating things the most. Synchronous and AsynchronousWhenever you build some piece of computer hardware you always have the choice of using either a synchronous or asynchronous bus. In the case of a synchronous bus there is a clock signal which sets the speed that everything happens at. Each clock pulse sets the timing for the entire data exchange on a bus and any device that connects to the bus has to be capable of working at this speed. An asynchronous bus uses signals generated by the devices connected to it to regulate the flow of data. In this case the bus may have a maximum speed but if a slow device needs more time to transfer data it can have it. In practice things are never this clear cut and engineers find ways of slowing down synchronous buses. For example, the CPU to memory bus uses “wait” cycles, in effect bus clock pulses when nothing happens, to allow slow memory chips to work with a faster processor. SerialOne final piece of jargon that you will encounter is the term “serial” bus. A serial bus just has one wire to transfer data and perhaps one or two additional wires to control the transfer. It is obvious that to send say a byte of data it is going to have to be broken down and sent bit-by-bit and then reassembled. However even if a bus has more than one wire, i.e. if it is a parallel bus, it is usually necessary to send data as multiple transfers. The distinction between a serial bus and a parallel bus is a fairly artificial one in this sense but there is a very different philosophy implied by the word “serial”. Until recently the best-known example of a serial bus was the RS232 socket on the back of most PCs. It didn’t really qualify as a bus because in general it could only connect two devices but today there are real serial buses that have mostly replaced it - USB and to a lesser extent FireWire or IEEE –1394. Because of their simplicity and because they don't have the drawback of signals leaking between multiple data lines a serial bus can achieve data transfer speed that exceed most parallel buses. Networks and BusesThere is a connection between networks and buses that is worth knowing about. When a bus can have multiple bus masters then the big problem is working out which one is the master at any given moment. The simplest solutions e.g. first come first served, do not work very well because of the problem of bus hogging. For example, if a graphics processor decided that it should download 100Mbytes of data and grabbed the memory bus then the user might just notice the rest of the machine come to a halt. One simple solution is to reduce the maximum amount of data that can be transferred in a single bus acquisition. This works but notice that in general the efficiency of a shared bus goes up with the size of the data block. Even so breaking data transfer up into packets is one of the main ways of sharing a bus between bus masters. Now you might begin to see the connection between a bus and a network. What else is a network than a bus with multiple bus masters? A network can be regarded as a serial bus with a sophisticated bus mastering scheme. What is important about this observation, apart from it being a new way of looking at things, is that as computers develop they are starting to make use of high speed bus architectures that look more like networks than traditional simple buses. When the processor wants to send some data to the memory it just sends a packet off, complete with a suitable address. The memory or any other device connected to the bus can pick up data that is addressed to it or send data to another device in the same way. The PCI bus and its sucessor the serial PCI Express bus has some of these characteristics in that any device can pass data to any other device but neither work fast enough to be the main bus connecting the processor to memory. Some experimental high-speed computers have been built using networking techniques to connect all of the machine’s components together. This is the way that PCs will be built in the future and then you will not only have a network outside of the box but inside as well. Related ArticlesCache Memory And The Caching Principle To be informed about new articles on I Programmer, sign up for our weekly newsletter, subscribe to the RSS feed and follow us on Twitter, Facebook or Linkedin.

Comments

or email your comment to: comments@i-programmer.info |

| Last Updated ( Sunday, 18 September 2022 ) |